# MCA-117/BCA-ED

# **Microprocessor and its Applications**

# Uttar Pradesh Rajarshi Tandon Open University

| Block-1 | INTRODUCTION TO MICROPROCESSOR                                    |                   |  |  |  |  |  |

|---------|-------------------------------------------------------------------|-------------------|--|--|--|--|--|

|         |                                                                   | 3-70              |  |  |  |  |  |

| UNIT-1  | Introduction to Microprocessor                                    | 7                 |  |  |  |  |  |

| UNIT-2  | Memory                                                            | 31                |  |  |  |  |  |

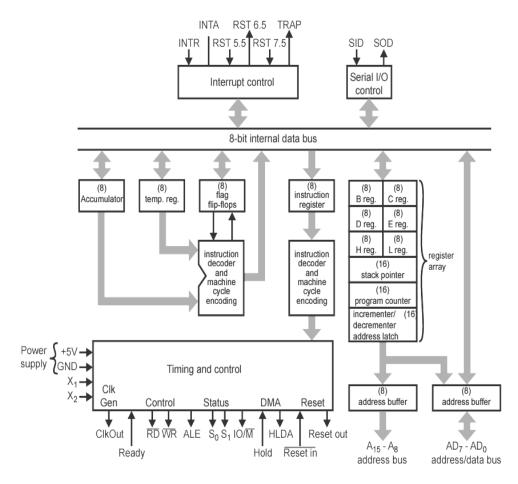

| UNIT-3  | Architecture of 8085 Microprocessor                               | 59                |  |  |  |  |  |

| Block-2 | OPERATIONS, INSTRUCTION SET<br>ASSEMBLY LANGUAGE PROGRAMMIN<br>71 | AND<br>NG<br>-132 |  |  |  |  |  |

| UNIT-4  | Operation and Control of 8085 Microprocesso                       | r 75              |  |  |  |  |  |

| UNIT-5  | Instruction Set of 8085 Microprocessor                            | 93                |  |  |  |  |  |

| UNIT-6  | Assembly Language Programming USING 8085                          | 5 111             |  |  |  |  |  |

| Block-3 | INTERFACE, INTERRUPT PROGRAMMABLE INTERFACE                       | AND               |  |  |  |  |  |

|         | 133-                                                              | -186              |  |  |  |  |  |

| UNIT-7  | Interfacing                                                       | 137               |  |  |  |  |  |

| UNIT-8  | Interrupts                                                        | 159               |  |  |  |  |  |

| UNIT-9  | Programmable Peripheral Interface                                 | 177               |  |  |  |  |  |

| Block-4 | TIMER, CONTROLLERS APPLICATIONS 189                               | AND<br>-256       |  |  |  |  |  |

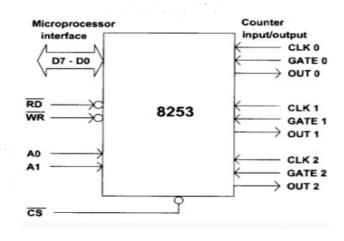

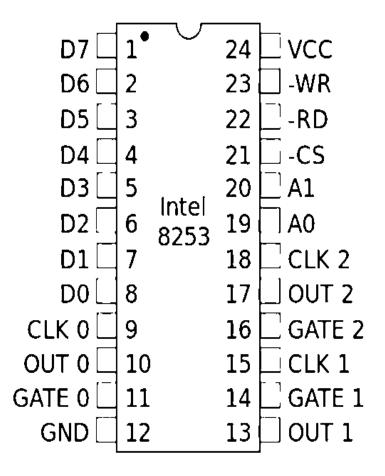

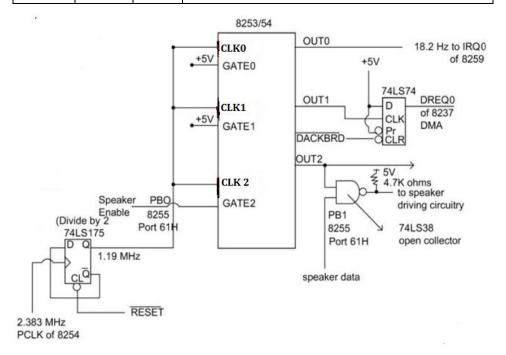

| UNIT-10 | Programmable Interval Timer-Intel 8253                            | 193               |  |  |  |  |  |

| UNIT-11 | Programmable Interrupt Controller 8253/825                        | 54 201            |  |  |  |  |  |

| UNIT-12 | Programmable interrupt Controller 8259A                           | 215               |  |  |  |  |  |

| UNIT-13 | Applications of Microprocessor                                    | 233               |  |  |  |  |  |

# MCA-117/BCA-ED

# Microprocessor and its Applications

# **BLOCK**

1

# INTRODUCTION TO MICROPROCESSOR

| UNIT-1                              |  |

|-------------------------------------|--|

| Introduction to Microprocessor      |  |

|                                     |  |

| UNIT-2                              |  |

| Memory                              |  |

|                                     |  |

| UNIT-3                              |  |

| Architecture of 8085 Microprocessor |  |

# **Course Design Committee**

Prof. Ashutosh Gupta Chairman

Director-In charge,

School of Computer and Information Science

UPRTOU, Prayagraj

Prof. U. S. Tiwari Member

Dept. of Computer Science

IIIT Prayagraj

Prof. R. S. Yadav Member

Department of Computer Science and Engineering

MNNIT-Allahabad, Prayagraj

Dr. Marisha Member

Assistant Professor (Computer Science)

School of Science, UPRTOU, Prayagraj

Mr. Manoj K. Balwant Member

Assistant Professor (Computer Science) School of Science, UPRTOU, Prayagraj

# **Course Preparation Committee**

Dr. Jeetendra Pande Author

**Assistant Professor**

Dept of Computer Science and Information Technology

Uttarakhand Open University, Haldwani

Prof. Ashutosh Gupta Editor

Director (In-charge)

School of Computer and Information Science

UPRTOU, Prayagraj

**Prof. Ashutosh Gupta**

Director (In-charge)

School of Computer and Information Science

UPRTOU, Prayagraj

Dr. Marisha (Coordinator)

Assistant Professor (Computer Science)

School of Science

UPRTOU, Prayagraj

©All Rights are reserved. No part of this work may be reproduced in any form, by mimeograph or any other means, without permission in writing from the **Uttar Pradesh Rajarshi Tondon Open University**, **Prayagraj**. Printed and Published by Dr. Arun Kumar Gupta Registrar, Uttar Pradesh Rajarshi Tandon Open University, 2019.

**Printed By :** Chandrakala Universal Pvt. 42/7 Jawahar Lal Neharu Road, Prayagraj.

# **BLOCK INTRODUCTION**

Computers and microprocessor based systems are a important part of the modern world. Aside from just the common desktop PC, there are a number of other types of specialized computer systems that pop up in many different places. The central component of these computers and computer systems is the microprocessor, or the CPU. The CPU is essentially the brains behind the computer system which is acutely involved in all the computations. This block is going to discuss what microprocessor units do, how they do it, and how they are designed. Unit 1 introduces evolution of microprocessor, internal components of a microprocessor and Number system. Unit 2 discusses about memory system. Unit 3 explains the internal architecture of Intel 8085 microprocessor in details.

# UNIT-1 INTRODUCTION TO MICROPROCESSOR

## 1.0 LEARNING OBJECTIVES

After going through this unit, you should be able to:

- Know the history of Microprocessor

- Define Microprocessor

- Know the internal architecture of a microprocessor

- Explain different types of busses

- Know different addressing techniques

- Perform decimal, binary and hexadecimal number conversions

- Define bit, byte and nibble

#### 1.1 INTRODUCTION

Prehistoric man used primitive tools were used for hunting, gathering, building, and animal husbandry<sup>1</sup>. The use of tools evolved as the needs of man did, and new tools were invented as new needs arose. These tools were used to craft the world as we know it today. Many types of tools have been created for the benefit of mankind. The invention of the computer is no exception. But the computer has not always been what we know it today.

The origin of modern computer is arguable. This is due in part to ambiguity of the word "computer." In general, a computer is something (or someone) that performs mathematical calculations. There are plenty of devices that fit this description ranging all the way back to the first known calculating device, the abacus. According to American Heritage Dictionary, a computer is "a device that computes, especially a programmable electronic machine that performs high-speed mathematical or logical operations or that assembles, stores, correlates, or otherwise processes information" (computer). The most commonly known form of a computer is, of course, the Personal Computer or PC. The modern PC is built almost entirely around one essential piece of hardware, the microprocessor.

The microprocessor is commonly described as the "brain" of any electronic device that employs it. It is the device that performs arithmetic

\_

creative common license

<sup>&</sup>lt;sup>3</sup> Image adopted from https://en.wikiversity.org/wiki/Hardware#/media/File:Computer2.png available under

and logical function at speeds that are many orders of magnitude faster than any human brain can perform. And, just as tools have evolved, many types of microprocessors have been invented to suite the many needs of man.

## 1.2 HISTORY

In the early 1960s, Fairchild Semiconductor and Texas instruments introduced the first commercially available integrated circuits (Warner). The integrated circuit(IC), revolutionized the electronics industry by placing multiple circuit components onto a miniaturized chip. The miniaturization of these components allowed for more complex circuits to be constructed. The increase in complexity of these chips can roughly be modeled by Moore's Law, which states that the amounts of transistors, the basic building block of digital electronics, will double every eighteen months (Moore's Law).

In 1971, Intel introduced the world's first single chip microprocessors which was invented by Intel engineers Federico Faggin, Ted Hoff, and Stan Mozor. Intel labeled it as 4004 Microprocessor that utilized the new silicon-gated MOS technology that many other engineers and scientist at that time believed that it was not yet possible for a single chip was able to contain the central processor unit (CPU), memory, input and output controls onto one, single chip. The chip was only 4-bit CPU, which compared to today's 64-bit microprocessors yet the microprocessor is still based on the same methods and designs even close to forty years later (Bellis).

In 1973, Texas instruments released their first single-chip microprocessor, the TI TMS 1000 yet it wasn't until 1974 in which the standalone version was create for mass production at \$2 apiece. Both the 4004 and the TI TMS 1000 chips were designed for use in calculators (Warner).

Intel was working on a new design, an upgraded model of the 4004 series, the 8008 which was introduced in mid 1972. The 8008 was considered to be the "first truly usable microprocessor (Warner)." The future upgrade in improvements in the memory and features such as improvements in stacks in the memory bank is what promised Intel a future in the microcomputer and microprocessor market with their development of the 8080 (Warner).

The demand for microprocessors increases rapidly. Ever since the early 1980s, new developments in technology have increased the desire as well as the performance for the use of microprocessors. The idea of a small electronic computing device that was easy and cheap to manufacture was incredibly popular. Eventually, engineers realized that the functionality of the microprocessor could be extended far beyond the scope of a calculator. Today, almost every electronic has some form of microprocessor control the electronics functions such as digital clocks,

televisions, MP3 Players, personal computers, cell phones, car ignitions, etc. All of these advancements have developed since the release of the original two chips.

# 1.2.2 Evolution of Intel Microprocessor Family

The evolution of Intel Microprocessor Family is summarized in the Table 1 below :

**Table 1: Evolution of Intel Microprocessor Family**

| Processor      | Year of  | No. of   | Clock   | Extern  | Interna | Addres |

|----------------|----------|----------|---------|---------|---------|--------|

|                | Introduc | Transist | Rate(M  | al Data | l Data  | s Bus  |

|                | tion     | or       | Hz)     | Bus     | Bus     |        |

| 4004           | 1971     | 2250     | 0.108   | 4       | 8       | 12     |

| 8008           | 1972     | 3500     | 0.200   | 8       | 8       | 14     |

| 8080           | 1974     | 6000     | 3       | 8       | 8       | 16     |

| 8085           | 1976     | 6000     | 6       | 8       | 8       | 16     |

| 8086           | 1978     | 29000    | 10      | 16      | 16      | 20     |

| 8088           | 1979     | 29000    | 10      | 8       | 16      | 20     |

| 80286          | 1982     | 134000   | 12.5    | 16      | 16      | 25     |

| 80386DX        | 1985     | 275000   | 33      | 32      | 32      | 32     |

| 80386SX        | 1988     | 275000   | 33      | 16      | 32      | 24     |

| Pantium        | 1993     | 3100000  | 66-200  | 64      | 32      | 32     |

| C              |          |          |         |         |         |        |

| Pantium        | 1997     | 4500000  | 300     | 64      | 32      | 32     |

| MMX<br>Pantium | 1995     | 5500000  | 200     | 64      | 32      | 36     |

| Pro            | 1993     | 3300000  | 200     | 04      | 32      | 30     |

| Pantium<br>II  | 1997     | 7500000  | 233-450 | 64      | 32      | 36     |

| Pantium<br>III | 1999     | 9500000  | 550-733 | 64      | 32      | 36     |

| Itanium        | 2001     | 30000000 | 800     | 128     | 64      | 64     |

| Pantium<br>IV  | 2002     | 42000000 |         |         |         |        |

# 1.3 MICROCOMPUTER AND MICROPROCESSORS

There are three major parts of a Computer System<sup>2</sup>.

- 1. Central Processing Unit (CPU): Also simply called as the microprocessor acts as the brain coordinating all activities within a computer.

- **2. The Memory :** A place where the program instructions and data are primarily stored.

- **3.** The Input/Output(I/O) Devices: Allow the computer to input information for processing and then output the results. I/O Devices are also known as computer peripherals.

The integrated Circuit (IC) chip containing the CPU is called the microprocessor and the entire computer including the microprocessor, memory and I/O is called a microcomputer.

#### **Activity:**

- 1. Using Internet, find the latest development of Intel Microprocessor family (Intel Pineview, Intel Wiskey lake, etc.).

- 2. Using Internet, find updates about the microprocess series of othe manufactures like Motorolla, AMD, etc.

# 1.4 INTERNAL ORGANIZATION OF A MICROCOMPUTER

<sup>&</sup>lt;sup>3</sup> Image adopted from https://en.wikiversity.org/wiki/Hardware#/media/File:Computer2.png available under creative common license

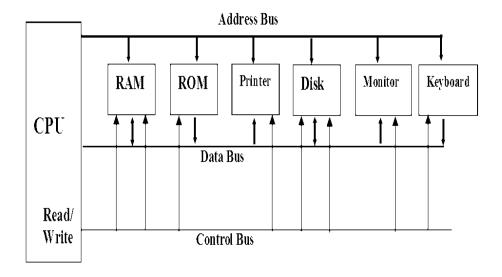

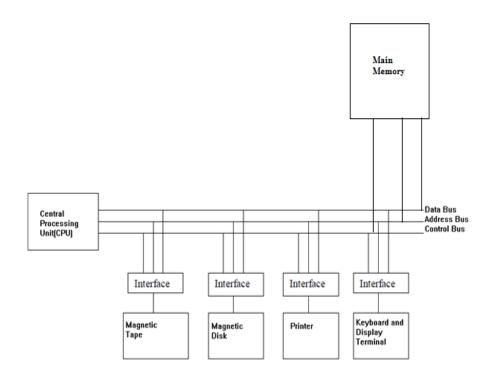

#### Figure 1: Internal organization of a microcomputer

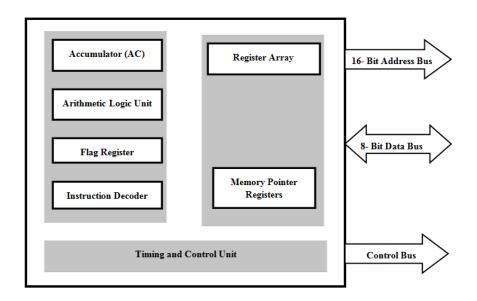

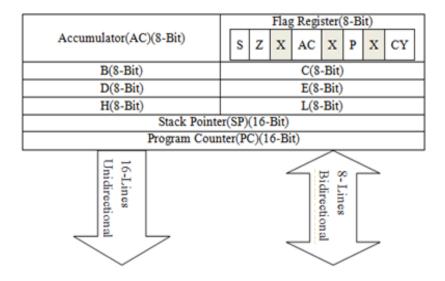

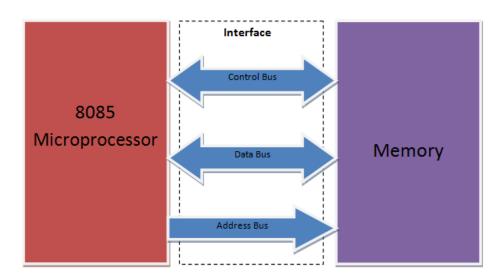

The CPU is connected to memory and I/O devices through a strip of wires called a bus. The bus inside a computer carries information from place to place. In every computer there are three types of busses:

- 1. Address Bus: The address bus is used to identify the memory location or I/O device the processor intends to communicate with. The width of the Address Bus rages from 20 bits (8086) to 36 bits for (Pentium II).

- **2. Data Bus:** Data bus is used by the CPU to get data from / to send data to the memory or the I/O devices. The width of a microprocessor is used to classify the microprocessor. The size of data bus of Intel microprocessors vary between 8-bit (8085) to 64-bit (Pentium).

- 3. Control Bus: How can we tell if the address on the bus is memory address or an I/O device address? This is where the control bus comes in (Figure 6). Each time the processor outputs an address it also activates one of the four control bus signals: Memory Read, Memory Write, I/O Read and I/O Write.

The address and control bus contains output lines only, therefore it is unidirectional, but the data bus is bidirectional.

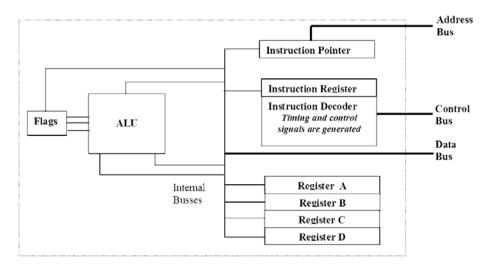

A program stored in the memory provides instructions to the CPU to perform a specific action. This action can be a simple addition. It is function of the CPU to fetch the program instructions from the memory and execute them.

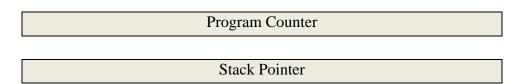

- 1. The CPU contains a number of registers to store information inside the CPU temporarily. Registers inside the CPU can be 8-bit, 16-bit, 32-bit or even 64-bit depending on the CPU.

- 2. The CPU also contains Arithmetic and Logic Unit (ALU). The ALU performs arithmetic (add, subtract, multiply, divide) and logic (AND, OR, NOT) functions.

- 3. The CPU contains a program counter also known as the Instruction Pointer to point the address of the next instruction to be executed.

- 4. Instruction Decoder is a kind of dictionary which is used to interpret the meaning of the instruction fetched into the CPU. Appropriate control signals are generated according to the meaning of the instruction.

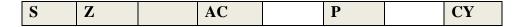

- 5. Accumulator is a Special Function Register(SFR) closely related to the operation of the ALU. It is a kind of working desk used for storing all data upon which some operation should be performed (addition, shift/move etc.). It also stores the results ready for use in further processing. One of the SFRs, called a Status Register (PSW), is closely related to the accumulator. It shows at any given

moment the "status" of a number stored in the accumulator (number is greater or less than zero etc.).

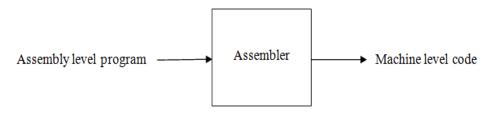

Figure 2: Internal block diagram of a CPU

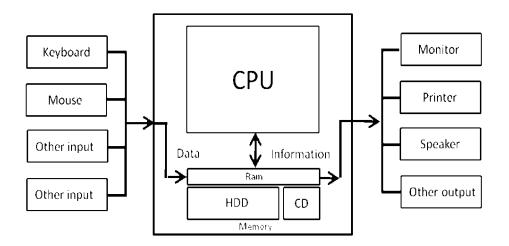

The Figure 3 below demonstrates the interaction between the CPU, memory and I/O Devices.

Figure 3: Interaction between the CPU, memory and I/O Devices inside a microcomputer<sup>3</sup>

#### 1.4.1 MEMORY UNIT

Memory is part of the microcomputer used for data storage. The easiest way to explain it is to compare it with a filing cabinet with many drawers. Suppose, the drawers are clearly marked so that it is easy to

<sup>&</sup>lt;sup>3</sup> Image adopted from https://en.wikiversity.org/wiki/Hardware#/media/File:Computer2.png available under creative common license

access any of them. It is easy enough to find out the contents of the drawer by reading the label on the front of the drawer.

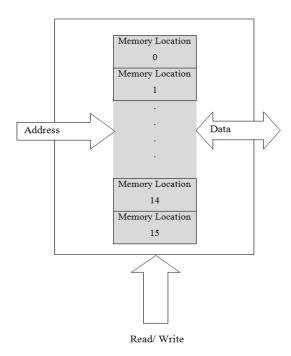

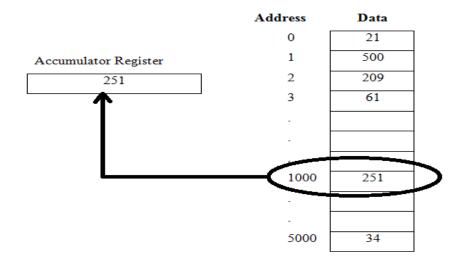

Figure 4: Memory

Each memory address corresponds to one memory location. The content of any location becomes known by its addressing(Figure 4). Memory can either be written to or read from.

#### 1.4.1.1 READ ONLY MEMORY (ROM)

ROM (Read Only Memory) is used to permanently save the program being executed. It is non-volatile in nature. The size of a program that can be written depends on the size of this memory. Today's microcontrollers commonly use 16-bit addressing, which means that they are able to address up to 64 Kb of memory, i.e. 65535 locations. As a novice, your program will rarely exceed the limit of several hundred instructions. There are several types of ROM.

- 1. **Masked ROM**: Microcontrollers containing this ROM are reserved for the great manufacturers. Program is loaded into the chip by the manufacturer. In case of large scale manufacture, the price is very low.

- 2. One Time Programmable ROM (OTP ROM): If the microcontroller contains this memory, you can download a program into this memory, but the process of program downloading is a "one-way ticket", meaning that it can be done only once. If an error is detected after downloading, the only thing you can do is to download the corrected program to another chip.

3. UV Erasable Programmable ROM (UV EPROM): Both the manufacturing process and characteristics of this memory are completely identical to OTP ROM. However, the package of this microcontroller has a recognizable "window" on the upper side(Figure 5). It enables the surface of the silicon chip inside to be lit by an UV lamp, which effectively erases and program from the ROM. Installation of this window is very complicated, which normally affects the price.

Figure 5: UV erasable programmable ROM<sup>4</sup>

- 4. **Flash memory:** This type of memory was invented in the 80s in the laboratories of INTEL and were represented as the successor to the UV EPROM. Since the contents of this memory can be written and cleared practically an unlimited number of times, the microcontrollers with Flash ROM are ideal for learning, experimentation and small-scale manufacture. Because of its popularity, the most microprocessor and microcontrollers are manufactured in flash versions today.

- 5. Electrically Erasable Programmable ROM (EEPROM): The contents of the EEPROM may be changed during operation (similar to RAM), but remains permanently saved even upon the power supply goes off (similar to ROM). Accordingly, an EEPROM is often used to store values, created during operation, which must be permanently saved. For example, if you design an electronic lock or an alarm, it would be great to enable the user to create and enter a password, but useless if it is lost every time the power supply goes off. The ideal solution is the microcontroller with an embedded EEPROM.

#### 1.4.1.2 RANDOM ACCESS MEMORY (RAM)

<sup>&</sup>lt;sup>4</sup> Image adopted from http://learn.mikroe.com/ebooks/picmicrocontrollersprogramminginassembly/front-matter/introduction-to-the-world-of-microcontrollers/ available under creative commons license.

Once the power supply is off the contents of RAM (Random Access Memory) is cleared and hence it is volatile in nature. It is used for temporary storing data and intermediate results created and used during the operation of the microcontroller. For example, if the program performs an addition (of whatever), it is necessary to have a register representing what in everyday life is called the "sum". For that purpose, one of the registers in RAM is called the "sum" and used for storing results of addition.

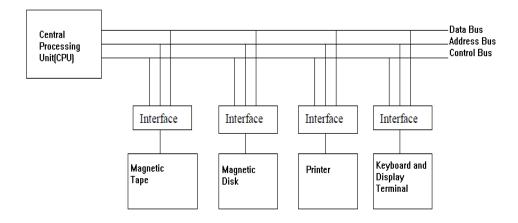

A CPU is referred to as the brain of the computer. For any processing on data, the data need to be brought inside the CPU. The data is transferred inside the CPU via input devices and the processed information is displayed via output devices. These input/output devices like, printer, keyboard, mouse, monitor, etc. are collectively known as Peripheral devices. At times the information is stored in the secondary storage devices for future reference. Clearly, the CPU needs to communicate with memory and peripheral devices. Therefore, the CPU requires some path, known as bus, through which it can communicate to these devices. Figure 6 shows how CPU is connected to these devices.

Figure 6: Processor Interconnection with Peripheral Devices

In Figure 6, the peripheral devices are connected to CPU via interface. There are many differences in the implementation of CPU and the peripherals devices, some of the major differences are listed below:

- 1. CPU is an electronic device whereas the peripheral devices are electromechanical (like printer, which have mechanical motors for page movement) and electromagnetic devices (like secondary memory). Therefore, the technology behind these two entities and the manner of operation is different.

- 2. CPU transmits and processes the data at very fast rate whereas the data transfer rate of peripheral devices is comparatively very slow.

- Moreover, CPU transmits the data in parallel whereas peripheral devices usually transmit data serially.

- 3. Data codes and formats in peripherals differ from the word format in the CPU and memory.

To overcome these mismatches, a special hardware, known as interface is connected between CPU and these peripherals device to take care of all the above issues and to supervise and synchronize all input and output transfers. These components are called **interface.**

CPU needs to communicate with memory and other peripherals devices. There are many peripheral devices attached to a computer, so to locate a specific device, an address is required. Similarly, to read/write data from/to memory, an address need to be specified. Also, CPU need to specify the control information i.e., what operation it has to perform. Like in case of memory, CPU needs to specify whether it is a read operation or a write operation. After specifying the address and the control information, the data need to be transferred between CPU and peripheral devices/memory. For this purpose, bus is required. Bus is a conducting path that connects the CPU with other devices. Based on the purpose for which the bus is used, it is categorised into three categories.

- a. *Address Bus:* An address bus is used by the CPU to transmit the address of the peripherals/memory location. Since, it is used by CPU only, this bus is unidirectional.

- b. *Control Bus:* It is used by the CPU to control and regulate the various devices attached to it. This bus is bidirectional.

- c. *Data Bus:* It is used by CPU and the devices attached to the CPU to transfer data. This Bus is bidirectional.

Apart from peripheral devices, the CPU is also connected to main memory and needs to frequently communicate with it. So, bus is also required to connect the CPU with memory. There are three possible architectures to connect the CPU with memory and peripheral devices.

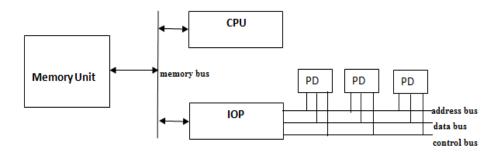

Different set of address, data and control buses are used to connect memory and other Peripheral Devices (PD), as shown in Figure 7.

In this case a separate Input/Output processor (IOP) is required to control the peripheral devices. The memory communicates with CPU and IOP using memory bus whereas the IOP communicates with its separate address data and control bus.

Figure 7: Interconnection of Peripheral Devices and Memory using different set of Buses

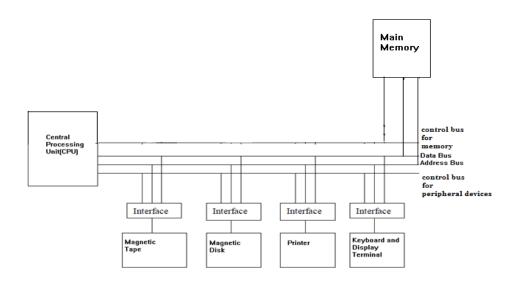

2. The second alternative is to connect CPU to memory and peripheral is using different set of control buses but data and address buses are common.

Figure 8 : Interconnection of CPU and Peripheral Devices using Common Address & Data Bus and different Control Buses

The same is shown in Figure 8. When CPU needs to communicate with memory or I/O device, it places the data in the data bus and

specifies the address using address bus. The distinction between I/O device and memory is made via control lines. If CPU wants to interact with memory, it will use the control lines dedicated for memory. This will isolate all the I/O devices and the memory will clearly recognize that the address is directed to memory, not I/O devices. Similarly, if CPU wants to interact with I/O devices, it will use the control lines dedicated for I/O devices. Whenever the CPU communicates with memory, the I/O device remains isolated and when CPU communicates with I/O devices, memory becomes isolated. Therefore this configuration is also known as Isolated I/O method.

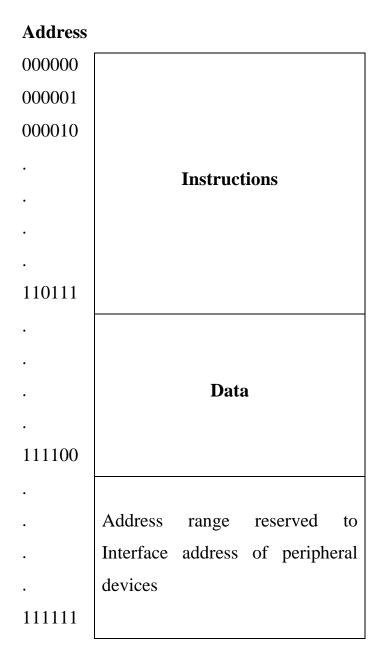

3. The third alternative is to use all the buses i.e., data, addresses and control bus to connect the CPU with peripheral and memory. The same is shown below in Figure 9.

Figure 9 : Interconnection of CPU and Peripheral Devices using Common Address, Data Bus Control Bus

In this case, some of the address range of the main memory is reserved to peripheral devices. This configuration is known as memory-mapped I/O. In this case, the CPU does not make any distinction between memory and peripheral devices and use the same set of read and write signals for both memory-read/ peripheral-read and memory-write/peripheral-write

operations as the interface of the peripheral devices are treated similar to memory address( refer Figure 10). Thus, this reduces the number of instructions in the instruction set of the computer as the same instructions can be used for memory as well as peripheral devices. The drawback of this scheme is, the memory cannot be fully utilized as some of the address from the address range of memory is reserved for peripheral address.

Figure 10: Address Range in Memory-Mapped I/O Configuration

#### 1.4.2 TIMERS/COUNTERS

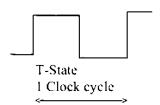

The microcomputer oscillator uses quartz crystal for its operation. Even though it is not the simplest solution, there are many reasons to use it. Namely, the frequency of such oscillator is precisely defined and very stable, the pulses it generates are always of the same width, which makes them ideal for time measurement. Such oscillators are used in quartz watches. If it is necessary to measure time between two events, it is sufficient to count pulses coming from this oscillator. That is exactly what the timer does.

#### 1.4.3 INPUT/OUTPUT PORTS

In order to make the microcomputer useful, it has to be connected to additional electronics, i.e. peripherals. Each microcontroller has one or more registers (called a "port") connected to the microprocessor pins. Usually, each I/O port is under control of another SFR, which means that each bit of that register determines the state of the corresponding microcontroller pin. For example, by writing logic one (1) to one bit of that control register SFR, the appropriate port pin is automatically configured as input. It means that voltage brought to that pin can be read as logic 0 or 1. Otherwise, by writing zero to the SFR, the appropriate port pin is configured as an output. Its voltage (0V or 5V) corresponds to the state of the appropriate bit of the port register.

### **Activity:**

1. Using Internet, find the address bus width of latest microprocessor architecture.

## 1.5 BASICS

#### 1.5.1 WORLD OF NUMBERS

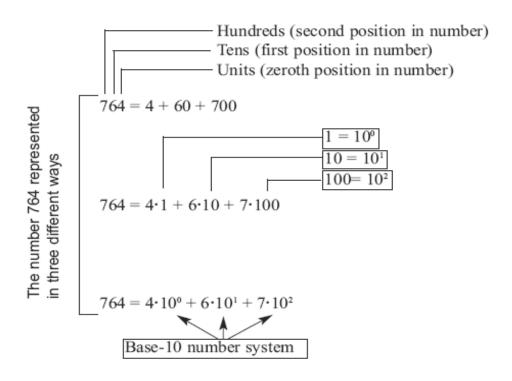

Mathematics is such a good science!<sup>5</sup> Everything is so logical and simple as that. The whole universe can be described with ten digits only. But, does it really have to be like that? Do we need exactly ten digits? Of course not, it is only a matter of habit. Remember the lessons from the school. For example, what does the number 764 mean: four units, six tens and seven hundreds. Simple! Could it be described in a bit more complicated way? Of course it could: 4 + 60 + 700. Even more complicated? Naturally: 4\*1 + 6\*10 + 7\*100. Could this number look a bit more scientific? The answer is yes:  $4*10^0 + 6*10^1 + 7*10^2$ . What does it actually mean? Why do we use exactly these numbers: 100, 101 and 102? Why is it always about the number 10? That is because we use ten different digits (0, 1, 2, ..., 8, 9). In other words, because we use base-10 number system, i.e. decimal number system.

http://learn.mikroe.com/ebooks/picmicrocontrollersprogramminginassembly/front-matter/introduction-to-the-world-of-microcontrollers/ available under creative commons license.

Figure 11: The number 764 represented in three different ways

#### 1.5.1.1 BINARY NUMBER SYSTEM

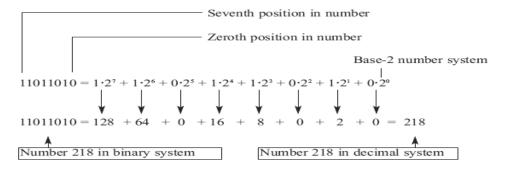

What would happen if only two digits would be used- 0 and 1? Or if we would not know to determine whether something is 3 or 5 times greater than something else? Or if we would be restricted when comparing two sizes, i.e. if we could only state that something exists (1) or does not exist (0)? Nothing special would happen, we would keep on using numbers in the same way, but they would look a bit different. For example: 11011010. How many pages of a book does the number 11011010 include? In order to learn that, follow the same logic like in the previous example, but in reverse order. Bear in mind that all this is about mathematics with only two digits- 0 and 1, i.e. base-2 number system (binary number system).

Figure 12: The number 218 represented in binary and decimal system

Clearly, it is the same number represented in two different ways(Figure 12). The only difference is in the number of digits necessary for writing some number. One digit (2) is used to write the number 2 in decimal system, whereas two digits (1 and 0) are used to write that number in binary system. Do you now agree that there are 10 groups of people? Welcome to the world of binary arithmetic! Do you have any idea where it is used?

Excepting strictly controlled laboratory conditions, the most complicated electronic circuits cannot accurately determine the difference between two sizes (two voltage values, for example) if they are too small (lower than several volts). The reasons are electrical noises and something called the "real working environment" (unpredictable changes of power supply voltage, temperature changes, tolerance to values of built in components etc.). Imagine a computer which would operate upon decimal numbers by recognizing 10 digits in the following way: 0=0V, 1=5V, 2=10V, 3=15V, 4=20V... 9=45V !? Did anybody say batteries? A far simpler solution is the use of binary logic where 0 indicates that there is no voltage and 1 indicates that there is voltage. It is easier to write 0 or 1 instead of "there is no voltage" or "there is voltage". It is called logic zero (0) and logic one (1) which electronics perfectly conforms with and easily performs all those endlessly complex mathematical operations. It is electronics which in reality applies mathematics in which all numbers are represented by two digits only and in which it is only important to know whether there is voltage or not. Of course, we are talking about digital electronics.

#### 1.5.1.2 HEXADECIMAL NUMBER SYSTEM

At the very beginning of computer development it was realized that people had many difficulties in handling binary numbers. Because of this, a new numbering system had to be established. This time, a number system using 16 different digits. The first ten digits are the same as digits we are used to  $(0, 1, 2, 3, \dots 9)$  but there are six digits more. In order to keep from making up new symbols, the six letters of alphabet A, B, C, D, E and F are used(Figure 13). A hexadecimal number system consisting of digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F has been established. What is the purpose of this seemingly bizarre combination? Just look how perfectly everything fits the story about binary numbers.

Figure 13: Binary and Hexadecimal number

The largest number that can be represented by 4 binary digits is the number 1111. It corresponds to the number 15 in decimal system. That number is in hexadecimal system represented by only one digit F. It is the largest one digit number in hexadecimal system. Do you see how skillfully it is used? The largest number written with eight digits is at the same time the largest two digit hexadecimal number. Bear in mind that the computer uses 8-digit binary numbers.

#### **1.5.2 CODES**

#### 1.5.2.1 BCD Code

BCD code is actually a binary code for decimal numbers only. It is used to enable electronic circuits to communicate in a decimal number system with peripherals and in a binary system within "their own world". It consists of four digit binary numbers which represent the first ten digits (0, 1, 2, 3 ... 8, 9). Even though four digits can give a total of 16 possible combinations, only the first ten are used.

#### 1.5.3 NUMBER SYSTEM CONVERSION

The binary numbering system is the most commonly used, the decimal system is the most understandable while the hexadecimal system is somewhere between them. Therefore, it is very important to learn how to convert numbers from one numbering system to another, i.e. how to turn a series of zeros and units into values understandable to us.

#### 1.5.3.1 BINARY TO DECIMAL NUMBER CONVERSION

Digits in a binary number have different values depending on their position in that number. Additionally, each position can contain either 1 or 0 and its value may be easily determined by its position from the right. To make the conversion of a binary number to decimal it is necessary to multiply values with the corresponding digits (0 or 1) and add all the results. The magic of binary to decimal number conversion works...You doubt? Look at the example:

$$(110)_2 = 1*2^2 + 1*2^1 + 0*2^0 = (6)_{10}$$

It should be noted that for decimal numbers from 0 to 3 you only need two binary digits. For greater values, extra binary digits must be added. Thus, for numbers from 0 to 7 you need three digits, for numbers from 0 to 15-four digits etc. Simply speaking, the largest binary number consisting of n digits is obtained when the base 2 is raised by n. The result should be then subtracted by 1. For example, if n=4:

$$2^4 - 1 = 16 - 1 = 15$$

Accordingly, using 4 binary digits it is possible to represent decimal numbers from 0 to 15, including these two digits, which amounts to 16 different values in total.

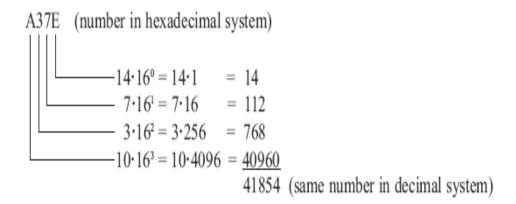

# 1.5.3.2 HEXADECIMAL TO DECIMAL NUMBER CONVERSION

In order to make conversion of a hexadecimal number to decimal, each hexadecimal digit should be multiplied with the number 16 raised by its position value. For example (see Figure 14):

Figure 14: Hexadecimal to decimal number conversion

#### 1.5.3.3 HEXADECIMAL TO BINARY NUMBER CONVERSION

It is not necessary to perform any calculation in order to convert hexadecimal numbers to binary numbers. Hexadecimal digits are simply replaced by the appropriate four binary digits(Figure 15). Since the maximum hexadecimal digit is equivalent to decimal number 15, we need to use four binary digits to represent one hexadecimal digit. For example:

$$E4 = \frac{11100100}{| \ \ |}$$

$$E = 4$$

Figure 15: Hexadecimal to binary number conversion

Figure 16 below contains the values of numbers 0-255 in three different numbering systems.

#### 1.5.4 MARKING NUMBERS

The hexadecimal numbering system is along with binary and decimal number systems considered to be the most important for us. It is easy to make conversion of any hexadecimal number to binary and it is also easy to remember it. However, these conversions may cause

confusion. For example, what does the statement "It is necessary to count up 110 products on assembly line" actually mean? Depending on whether it is about binary, decimal or hexadecimal, the result could be 6, 110 or 272 products, respectively! Accordingly, in order to avoid misunderstanding, different prefixes and suffixes are directly added to the numbers. The prefix \$ or 0x as well as the suffix h marks the numbers in hexadecimal system. For example, hexadecimal number 10AF may look as follows \$10AF, 0x10AF or 10AFh. Similarly, binary numbers usually get the suffix % or 0b, whereas decimal numbers get the suffix D.

| DEC. | BINARY |   |   |   |   | HEX. |   |   |    |

|------|--------|---|---|---|---|------|---|---|----|

| 0    | 0      | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0  |

| 1    | 0      | 0 | 0 | 0 | 0 | 0    | 0 | 1 | 1  |

| 2    | 0      | 0 | 0 | 0 | 0 | 0    | 1 | 0 | 2  |

| 3    | 0      | 0 | 0 | 0 | 0 | 0    | 1 | 1 | 3  |

| 4    | 0      | 0 | 0 | 0 | 0 | 1    | 0 | 0 | 4  |

| 5    | 0      | 0 | 0 | 0 | 0 | 1    | 0 | 1 | 5  |

| 6    | 0      | 0 | 0 | 0 | 0 | 1    | 1 | 0 | 6  |

| 7    | 0      | 0 | 0 | 0 | 0 | 1    | 1 | 1 | 7  |

| 8    | 0      | 0 | 0 | 0 | 1 | 0    | 0 | 0 | 8  |

| 9    | 0      | 0 | 0 | 0 | 1 | 0    | 0 | 1 | 9  |

| 10   | 0      | 0 | 0 | 0 | 1 | 0    | 1 | 0 | Α  |

| 11   | 0      | 0 | 0 | 0 | 1 | 0    | 1 | 1 | В  |

| 12   | 0      | 0 | 0 | 0 | 1 | 1    | 0 | 0 | С  |

| 13   | 0      | 0 | 0 | 0 | 1 | 1    | 0 | 1 | D  |

| 14   | 0      | 0 | 0 | 0 | 1 | 1    | 1 | 0 | E  |

| 15   | 0      | 0 | 0 | 0 | 1 | 1    | 1 | 1 | F  |

| 16   | 0      | 0 | 0 | 1 | 0 | 0    | 0 | 0 | 10 |

| 17   | 0      | 0 | 0 | 1 | 0 | 0    | 0 | 1 | 11 |

| •••• |        |   |   |   |   |      |   |   |    |

|      |        |   |   |   |   |      |   |   |    |

| 253  | 1      | 1 | 1 | 1 | 1 | 1    | 0 | 1 | FD |

| 254  | 1      | 1 | 1 | 1 | 1 | 1    | 1 | 0 | FE |

| 255  | 1      | 1 | 1 | 1 | 1 | 1    | 1 | 1 | FF |

Figure 16: Conversion table<sup>6</sup>

#### 1.5.5 BIT

Theory says a bit is the basic unit of information. Let's forget this dry explanation for a moment and take a look at what it is in practice. The answer is nothing special a bit is a binary digit. Similar to decimal number system in which digits in a number do not have the same value ( for example digits in the number 444 are the same, but have different values),

<sup>&</sup>lt;sup>6</sup> Adopted from

the "significance" of the bit depends on the position it has in the binary number. Therefore, there is no point talking about units, tens etc. Instead, here it is about the zero bit (rightmost bit), first bit (second from the right) etc. In addition, since the binary system uses two digits only (0 and 1), the value of one bit can be 0 or 1.

Don't be confused if you find some bit has value 4, 16 or 64. It means that bit's values are represented in decimal system. Simply, we have got so much accustomed to the usage of decimal numbers that these expressions became common. It would be correct to say for example, "the value of sixth bit in binary number is equivalent to decimal number 64".

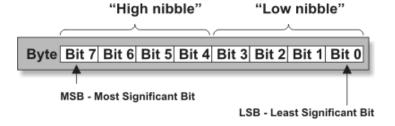

#### 1.5.6 **BYTE**

A byte or a program word consists of eight bits grouped together. If a bit is a digit, it is logical that bytes represent numbers. All mathematical operations can be performed upon them, like upon common decimal numbers. As is the case with digits of any other number, byte digits do not have the same significance. The largest value has the leftmost bit called the most significant bit (MSB). The rightmost bit has the least value and is therefore called the least significant bit (LSB). Since eight zeros and units of one byte can be combined in 256 different ways, the largest decimal number which can be represented by one byte is 255 (one combination represents zero).

A nibble is referred to as half a byte. Depending on which half of the byte we are talking about (left or right), there are "high" and "low" nibbles(see Figure 17).

Figure 17: High and Low nibbles<sup>7</sup>

## 1.6 SUMMARY

- 1. 1946 The first generation of Computer ENIAC was started to be used on the vacuum tube technology.

- 2. 1958 The first transistorized computer TRADIC was announced by IBM.

http://learn.mikroe.com/ebooks/picmicrocontrollersprogramminginassembly/front-matter/introduction-to-the-world-of-microcontrollers/

<sup>&</sup>lt;sup>7</sup> Adopted from

- 3. 1959 The first IC was invented.

- 4. 1960s ICs were started to be used in CPU boards.

- 5. 1970s entire CPU was put in a single chip. (1971 the first microprocessor of Intel 4004 with 4-bit data bus and around 2300 transistors was introduced).

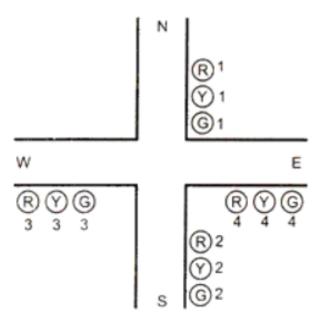

- 6. Late 1970s Intel 8080/85 appeared with 8-bit data bus and 16-bit address bus and used from traffic light controllers to homemade computers.1981 First PC was introduced by IBM Intel 8088 microprocessor.

- 7. Motorola emerged with 6800. Apple Macintosh computers started to use 68000 series of microprocessors.

- 8. The increase in complexity of these chips can roughly be modeled by Moore's Law, which states that the amount of transistors, the basic building block of digital electronics, will double every eighteen months.

- 9. A program stored in the memory provides instructions to the CPU to perform a specific action.

- 10. Memory is part of the microcomputer used for data storage.

- 11. Each memory address corresponds to one memory location.

- 12. A CPU is referred to as the brain of the computer. For any processing on data, the data need to be brought inside the CPU. The data is transferred inside the CPU via input devices and the processed information is displayed via output devices.

- 13. The peripheral devices are connected to CPU via interface.

- 14. CPU needs to communicate with memory and other peripherals devices. There are many peripheral devices attached to a computer, so to locate a specific device, an address need to be specified.

- 15. Binary number system deals with only two digits- 0 and 1.

- 16. Digits in a binary number have different values depending on their position in that number.

- 17. Hexadecimal number system use 16 different digits. The first ten digits are the same as digits we are used to (0, 1, 2, 3,... 9) but there are six digits more. In order to keep from making up new symbols, the six letters of alphabet A, B, C, D, E and F are used.

- 18. Binary Coded Decimal(BCD) code is actually a binary code for decimal numbers only.

- 19. Bit is the basic unit of information and it stands for Binary Digit.

- 20. A byte or a program word consists of eight bits grouped together.

# 1.7 CHECK YOUR PROGRESS

#### Fill in the blanks

| 1. | IC stands for                                                                                                            |

|----|--------------------------------------------------------------------------------------------------------------------------|

| 2. | The CPU is connected to memory and I/O devices through a strip of wires called a                                         |

| 3. | The address and control bus contains output lines only, therefore it is, but the data bus is                             |

| 4. | SPR stands for                                                                                                           |

| 5. | shows at any given moment the "status" of a number stored in the accumulator (number is greater or less than zero etc.). |

| 6. | The input/output devices like, printer, keyboard, mouse, monitor, etc. are collectively known as devices.                |

# Answers to fill in the blanks

- 1. Integrated circuit.

- 2. Bus

- 3. Unidirectional, bidirectional

- 4. Special Function Register

- 5. Program Status Word

- 6. Peripheral

# 1.8 MODEL QUESTIONS

- 1. What is a computer?

- 2. Define microprocessor.

- 3. State Moor's law,

- 4. What are the major components of a microcomputer system?

- 5. What is an accumulator?

- 6. With a help of a diagram, demonstrates the interaction between the CPU, memory and I/O Devices.

- 7. Explain the difference between OTP ROM and UV erasable programmable ROM.

- 8. List out the differences in the implementation of CPU and the peripherals devices.

- 9. Explain the three possible architectures to connect the CPU with memory and peripheral devices.

- 10. What is a timer? Why it is used in a microcomputer?

# **UNIT-II MEMORY**

## 2.0 LEARNING OBJECTIVES

After reading this unit, the learner should be able to:

- Know the development of memory

- Explain the working of D- flip flop

- Explain the working of m-bit register

- Explain the development of memory chips

- Explain memory read/write operations

- Classify RAM, ROM, PROM, EPROM and SRAM

- Explain the characteristics of memory

- Calculate the access time of the memory

- Explain the architecture of Intel 2716 ROM, Intel 6116 RAM, Dynamic RAM and 4116 DRAM

## 2.1 INTRODUCTION

Memory is a storage device. It stores program data and the results. There are two kind of memories; semiconductor memories & magnetic memories<sup>8</sup>. Semiconductor memories are faster, smaller, and lighter and consume less power. Semiconductor memories are used as the main memory of a computer. Magnetic memories are slow but they are cheaper than semiconductor memories. Magnetic memories are used as the secondary memories of a computer for bulk storage of data and information's. With the development in technology, semiconductor memories are used everywhere. Let us see how semiconductor memories are developed.

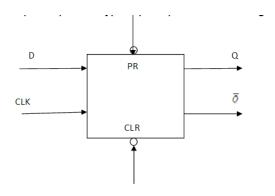

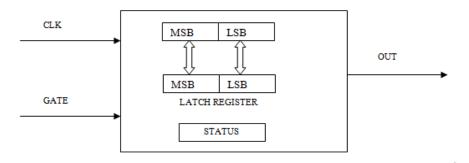

## 2.2 DEVELOPMENT OF MEMORY

The smallest unit of information in a digital system is a binary digit which has a logic value of 0 or 1. A bit of data is stored in electronics devices called a flip – flop or a 1-bit register. A flip – flop is a general memory and has two stable states in which it can remain indefinitely as long as the operating power is not interrupted. The output can be changed only if the input signals allow for it. A very simple type of flip – flop is D-type flip- flop as shown in Figure 18.

$<sup>^{8}</sup>$  Adopted from http://nptel.ac.in/courses/108107029/4 available under creative commons license.

Figure 18: D-Filp flop

It has a single data input D and two input, Q and Q. Output Q represents the state of flip- flop;  $\overline{Q}$  represent the complement of the flip- flop's state. The logic value at a flip- flop's D input when a clock signal, CLK occurs is stored in the flip- flop. If the store value is equal to 1 (Q = 1) the flip- flop is set. If the stored value is equal to 0 (Q = 0) the flip – flop is clear.

The logical operation of a D type flip – flop is expressed by the characteristic equation  $Q_{n+1} = D_n$ . This equation indicates that the output of a D- type flip – flop after the accordance of a clock pulse,  $Q_{n+1}$  is equal to the logic value of the D – input before the accordance of the clock pulse  $D_n$ .

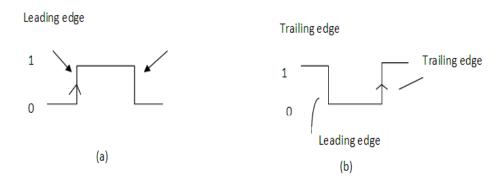

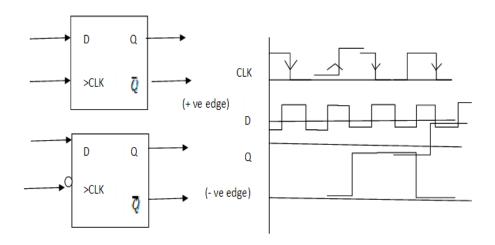

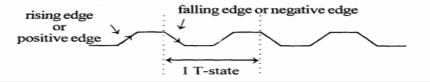

But D – type flip-flop differ with regard to the praise time at which the clock pulse causes the input data to be accepted, the output to change in accordance with the input, and the output to be held or latched. Two clock pulse or strokes are shown in **Figure 19**. The signal shown figure 19(a) signal is logic 0 in its quiescent state, makes a transition to logic 1 remains at logic 1 momentarily, and then returns to logic 0. The leading edge of the pulse is a 0 to 1 or positive transition and the trailing edge is a 1 to 0 or negative transition. The clock pulse shown in Figure 19(b) is a negative clock pulse, its quiescent value is logic 1 and it makes a momentary negative transition to logic 0 followed by a positive transition back to logic 1. A positive transition is also referred to as a using edge, and a negative transition is also referred as the following edge.

Figure 19: Leading and trailing edge of a pulse

An edge triggered D – type flip-flop latches the logic value at the D input during the clock pulse's transition from one logic value to the other. The sensitivity of the flip-flop to the transition (edge) of the clock is indicated on the flip-flop logic symbol by a dynamic indicator, a triangle <, at the clock input. Positive edge triggered flip – flops latch on the positive transition of the clock. Negative edge triggered Flip-flop/ latch on the negative transition of the clock. If the clock pulse of Figure 19 (a) is applied to the +ve edge pulse triggered flip-flop, the data is latched at the trailing edge of the pulse. If the clock pulse of Figure 19(b) is applied to a +ve edge triggered flip-flop, the data is latched at the trailing edge of the pulse. Note that in the edge triggered flip-flop, the input is accepted, and the output changes and is latched during a single clock transition (**Figure 20**).

Figure 20: +ve and -ve edge triggered flip flop

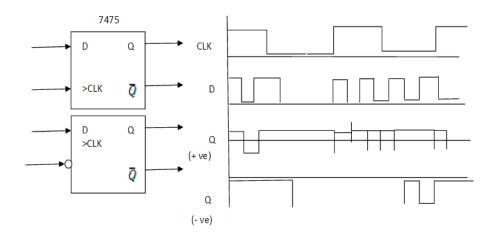

A level triggered flip-flop usually referred to simply as a latch has a clock input that is sensitive to the level of the clock signal. The output of a positive level triggered D flip-flop follows the D input when the clock signal is high. When the edge makes a transition from 1 to 0, the data present at the D input is latched. The output of a negative level triggered D flip-flop follows the input. When the clock is logic '0' and latches the input on a 0 to 1 transition. Thus for a level triggered flip-flop, the output follows the input, when the clock is at the trigger level. During this condition the flip-flop is referred to as being the input data is latched on the transition from the trigger level to the quiescent level.

Figure 21: Level Trigring

The D flip-flop shown two additional inputs common to most ICs are preset & clear. Both the input is active low signals. Preset & clear are asynchronous input; they affect the state of the flip-flop independent of the clock's level or transition(Figure 21). Thus preset & clear have over side influence on clock & synchronous input. Logic '0' at the clear input clears it for proper operation. Preset & clear are not absorbed simultaneously.

# 2.3 EXAMPLES OF LATCHES

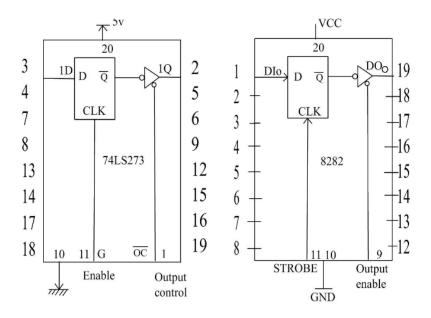

Typical examples of transparent latches ICs are 74LS373 & the Intel 8282 shown in **Figure 22** Both are functionally similar; however, they are not pin compatible. These octal latches are suitable to latch 8-bit data.

Figure 22 : Latches

#### **Function table**

| Output  | Enable | Input | Output |

|---------|--------|-------|--------|

| control | G      |       |        |

| L       | Н      | Н     | Н      |

| L       | Н      | L     | L      |

| L       | L      | X     | Q      |

| Н       | X      | Χ     | Hi     |

|         |        |       | edge   |

|        | STB | Input | O/P             |

|--------|-----|-------|-----------------|

| enable |     | DI    |                 |

| L      | Н   | Н     | Н               |

| L      | Н   | L     | L               |

| L      | L   | X     | D type<br>latch |

| Н      | X   | X     | L               |

These devices include eight D latches with tri-state buffers. They require

- two input signals,

- enable (G), and

- ( $\overline{OE}^-$ ) the output control for the 74LS373

which are synchronous to the stroke (STB) & the output control (OE<sup>-</sup>) for the 82072. The enable is an active high signal connected to the clock signal input of the flip-flop. When this signal goes low data are latched from the data bus. When the output control is low (active) the data latched is accessible to the display devices.

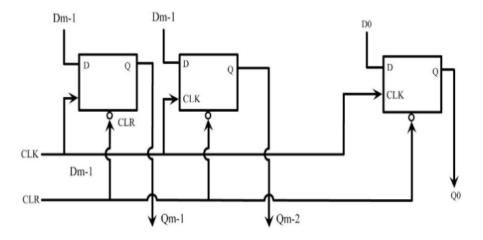

#### 2.3.1 M-BIT REGISTER

Memory is storage device and it is used to store both instructions and data. The smallest unit of information a digital system can store is a binary digit which has a logic value of '0' and '1'. A bit of data is stored in a flip flop. It is general memory cell and has two states in which it can remain indefinitely as long as power is not interrupted. The output can be changed only if the output signals allow for it. D flip flop is the simplest flip flop to store one bit of information. To store several bits(m-bits) of data simultaneously(**Figure 23**), the clock inputs of several D flip-flops are connected in parallel to form an m bit register (m may be 4, 6 or 8). Such registers store m bits of data  $D_0$  to  $D_{m-1}$  under the control of the clock and provide m bits of data output  $Q_0$  to  $Q_{m-1}$ .

The act of storing data in a register is a writer operation. Determining the value of the content of a register is a read operation.

Figure 23: m-bit register

The m- bit of data stored in a register make up a word. A word is simply a number of contiguous bits operated upon or considered by the hardware as a group. The number of bit in the word m is a word length. The m input to the register are provided by an m- bit input data bus and the m-output by an m- bit output data bus. A bus is a number of signal line grouped together because of similarity of function, which connect two or more systems or subsystem. Eight bit register are often called octal registers. Several equal length registers can be incorporated in a single IC and share a common set of inputs, a common set of outputs and a single clock. Such as circuit is referred to as a memory. Each register occupies a distinct location, which has a unique numerical address. Thus, memory can be thought of as a collection of addressable registers. Logic is necessary to decode address inputs to ensure that only a single register outputs its contents when data is being read from the memory, and only a single register has data stored in it when the data is being written into the memory.

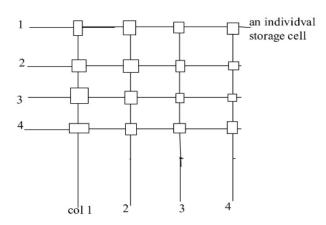

#### 2.3.2 DEVELOPMENT OF MEMORY CHIP

Let us consider a memory of 16 words, each of 8 bits is to be stored. 16 words can be stored in 16 memory locations, each having a unique 4 bit memory address (0000 to 1111) and each location being capable of containing 8 bits of data.

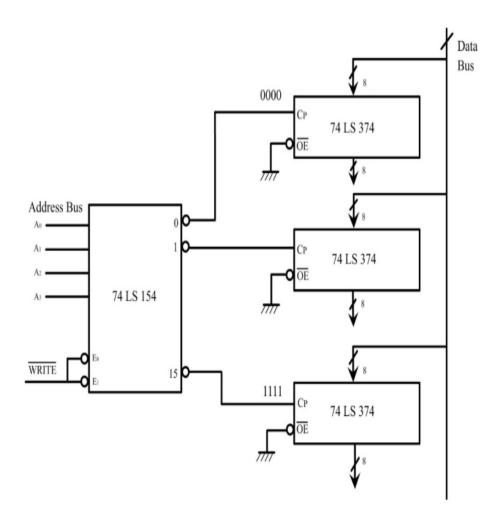

To set up this memory system using ICs, 16 bit flip-flop registers are required. To identify the correct address a 4 line-16 line decoder can be used to decode the 4 bit location address to select the appropriate data register (1 to 16) for input/output. **Figure 24**shows the circuit used to implement the memory system.

Figure 24: Memory system

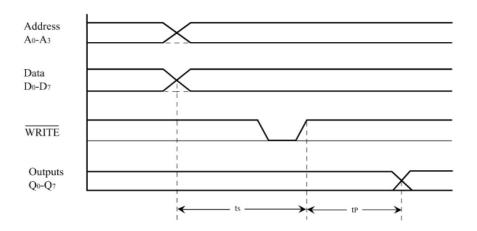

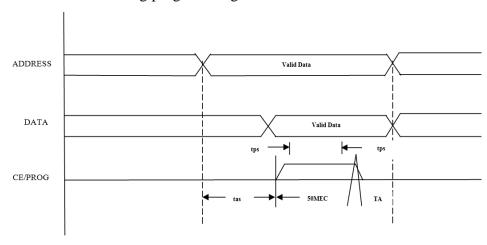

The 74LS374s are octal D flip flops with three state of outputs. To store data in them, 8 bits of data are put on the  $D_0$  to  $D_7$  data inputs via the data bus. Then the low to high edge on the clock input will cause the data  $D_0$  to  $D_7$  to be latched into each flip-flop. The stored value in the D flip-flop is observed at the outputs  $Q_0$  to  $Q_7$  by making the output enable  $(\overline{OE})$  pin low. To select the appropriate memory location, a 4 bit address is input to 74154 (4 Line to 16 Line decoder), which outputs a low pulse on one of the output lines when  $\overline{WRITE}$  is pulsed low. The timing of setting up the address bus, data bus and pulsing the  $\overline{WRITE}$  line is critical. The following **Figure 25** shows standard timing diagram bus driven devices. Rather than showing all four address lines and all data lines, they are grouped and X is used to show where any or all of the lines are allowed to change digital levels.

Figure 25: Timing diagram

The address and the data lines must be set up some time  $(t_s)$  before the low to high edge of  $\overline{WRITE}$ . In other words the address and the data lines must be valid some period of time  $(t_s)$  before the low to high edge of  $\overline{WRITE}$  in order for the 74374 to interpret them correctly.

When the  $\overline{WR\,ITE}$  line is pulsed, the decoder outputs a low pulse on one of its 16 outputs which clocks the appropriate memory location to receive data from the data bus. After the propagation delay,  $(t_p)$  the data output at  $Q_0$  to  $Q_7$  will be the new data just entered into the D flip-flop. Then the  $t_p$  will include the propagation delay of decoder and of the D flip-flop.

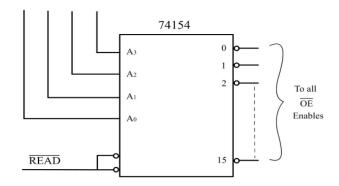

In the figure all the three state outputs are continuously enabled so that their Q outputs always active. To reduce the number of lines the 8 outputs  $Q_0$  to  $Q_7$  of all 16 memory locations back to the data bus. The  $\overline{OE}$  enables of the 16 memory locations have to be individually selected at the appropriate time to avoid a conflict on the data bus, called bus contention. Bus contention occurs when two or more devices are trying to send their digital levels to the shared data bus at the same time. To individually select each group of Q outputs, the grounds on the  $\overline{OE}$  enables would be removed and instead be connected to the output of another 74154 1 of 16 decoder.

Figure 26: 1 to 16 decoder

### 2.4 MEMORY

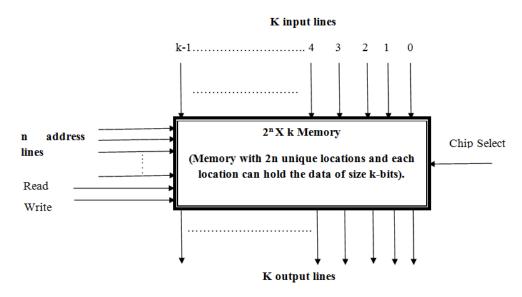

If a memory stores N- words of information each word being of m bits, we say it is a N X m memory. e.g. 8x4 memory means there are 8 words 4 each word containing 4- bit of information (called nibble). 8 words are stored at 8-memory locations and these memory locations are clearly identified by addresses. Addresses are formulated by bit combinations available in wires known as address lines. To identify 8 memory locations we require 3 address lines designed  $A_2A_1A_0$ . The memory locations identify and the corresponding content stored is shown in Table 2.

| <b>A</b> <sub>2</sub> | A <sub>1</sub> | <b>A</b> <sub>0</sub> | Decimal<br>Equivalent | Memory<br>Location | Contents of the memory location |

|-----------------------|----------------|-----------------------|-----------------------|--------------------|---------------------------------|

| 0                     | 0              | 0                     | 0                     | 0                  | M(0)                            |

| 0                     | 0              | 1                     | 1                     | 1                  | M(1)                            |

| 0                     | 1              | 0                     | 2                     | 2                  | M(2)                            |

| 0                     | 1              | 1                     | 3                     | 2                  | M(3)                            |

| 1                     | 0              | 0                     | 4                     | 3                  | M(4)                            |

| 1                     | 0              | 1                     | 5                     | 5                  | M(5)                            |

| 1                     | 1              | 0                     | 6                     | 6                  | M(6)                            |

| 1                     | 1              | 1                     | 7                     | 7                  | M(7)                            |

Table 2: The memory locations and the corresponding content

M(0) is the content of memory location '0'. It has 4 bits here. M(1) is the content of memory location '1' and so on.

The three address lines  $A_2A_1A_0$  together is known as address bus. It is a unidirectional bus. The microprocessor always sends the addresses.

In general, a N X m memory shall have K address lines designated  $A_{k-1}A_{k-2}A_{k-3}...$   $A_2A_1A_0$ , such that K is the smallest integer satisfying the inequality  $2^k \ge N$ . e.g. 200 X 8 memory shall have

200 memory locations each containing 8 bit of information. To identify 200 memory locations we require a minimum of K=8 lines designated  $A_7A_6A_5A_4A_3A_2A_1A_0$ . However K=8 address lines can identify a total of 256 memory location starting from  $(0000\ 0000)_2$  to  $(1111\ 1111)_2$  or  $00_H$  to  $FF_H$ . But we are using only 200 memory locations and rest locations are redundant. The 200 memory location shall be identified starting from  $(0000\ 0000)_2$  to  $(1110\ 0111)_2$  or  $00_H$  to  $C7_H$ . The other combinations  $(11101000)_2$  to  $(1111\ 1111)_2$  or  $C8_H$  to  $FF_H$  are not used in this memory & are redundant addresses.

Since it is too tiring & boring to use binary numbers for identifying the addresses we normally make use of hexadecimal number notation. E.g. 200 memory location are identified starting from (00)<sub>H</sub> to (C7)<sub>H</sub>, (C8)<sub>H</sub> to(FF)<sub>H</sub> are redundant memory locations. Using 10 address lines

designated  $A_9A_8A_7$ ...... $A_2A_1A_0$ , we can directly address  $2^{10}$ = 1024 memory locations. This is conventionally known as 1K memory locations.

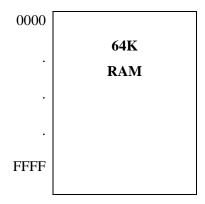

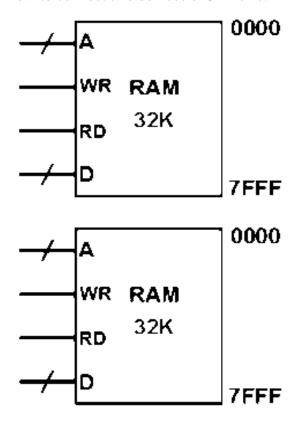

The capacity of a memory is specified terms of the maximum number of words the memory can store. In general, if the memory has an R bit address and each word is of length m, then the memory has a capacity of  $2^R$  X m bits, organized as  $2^K$  words each of m bits. If R=10, then the memory can store 1024 words or 1K words. In most of the 8 bit Microprocessor the Microprocessors has 16 address lines. Therefore it can address directly

- $2^{16}$ memory locations =  $2^6 \times 2^{10}$ memory locations

- = 64 K memory locations

- = 65536.

Thus, 8-bit microprocessor provides a maximum of  $2^{16}$  or 64 K memory addresses ranging from 0000 to FFFF<sub>H</sub>.

### 2.4.1 CHARACTERISTICS OF MEMORY

An important characteristic of a memory is whether it is volatile or non volatile. The contents of volatile memory are lost if the power is turned off. On the other hand, a non volatile memory retains its contents after the power is switched off. The best known non volatile memory is magnetic core.

In the broad sense, a Microprocessor's memory system can be logically divided into three groups:

- 1. Processor memory

- 2. Primary or main memory

- 3. Secondary memory

Processor memory refers to a set of Microprocessor registers. These registers hold temporary results when a computation is progress. There is no speed disparity between these registers and the Microprocessor because they are fabricated on the same chip using the same technology.

Primary memory is the external memory to store both program and data. The Microprocessor can access their memories directly. In earlier days, the primary memory was designed using magnetic cores. In modern Microprocessor s, MOS technology is employed in the primary memory design. Usually, the size of primary memory is much larger than the processor memory and its operating speed is slower than that the processor registers by a factor of 25 or 30.

Secondary memory refers to the storage medium compositing slow devices such as hard disks and floppies. These devices are used to hold large data and huge program that are not needed by the processor frequently. Sometimes, secondary memories are also referred to as auxiliary or back up storage.

In order to design an efficient memory system, the following characteristics of memory must be known. The most important factor of a memory system is its cost, expressed in Rupees per bit. A good design implies a very low cost per bit.

There are two parameters that will indicate the speed with which information can be transferred in and out of a memory.

- 1. Access time,  $t_A$

- 2. Cycle time, t<sub>C</sub>

The access time  $t_A$  is defined as the average time taken to read a unit of information from the memory. Sometimes the access time is also referred to as read access time. Similarly, one can define write access time. Usually, the write access time will be equal to read access time. The cycle time  $t_C$  of a memory unit is defined as the average time lapse between two successive read operations.

The reciprocal of access time is called the access rate  $(r_A=1/t_A)$ , which is expressed in bits per second. Similarly, the reciprocal of cycle time is referred to as date transfer rate or bandwidth also expressed in bits per second.

The third important characteristic of memory unit is its access mode. The access mode refers to the manner in which information can be accessed from the memory. There are two major access modes. They are the random access mode and sequential access modes. In random access mode, any memory location access time is independent of the location from which the date is read. In sequential access mode, the memory is accessed strictly in a sequential manner. In this mode, the access time depends on the location in which data is stored. They are also referred as serial access memories. A bipolar memory and magnetic tape are typical example for random & serial –access memories.

Some memories combine both access modes and called semi-random memories. A typical example is magnetic access with one read/write head for each track. This arrangement permits any track to be accessed. At random however, access within a track must be made in a serial fashion.

### 2.4.2 CLASSIFICATION OF MEMORY

In general, semiconductor memories can be clarified in two main groups' random access memories (RAM) and sequential access memories (SAM).

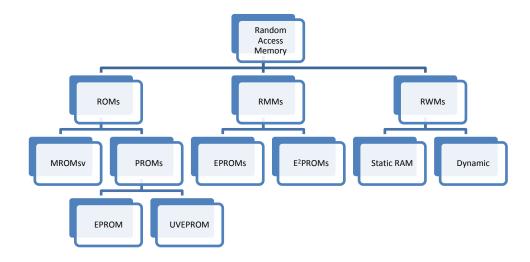

RAM can be classified in three main groups as shown below in **Figure 27**.

Figure 27: Classification of RAM

- 1. ROM: The type of memory means the content of an address location can only be read and cannot be written into. The contents of the memory location are not destroyed whether the power is ON or OFF. Such a memory is known as non-volatile memory. ROMs are used to store data on permanent basis. They are random access memories and this makes them very useful for the storage of computer operating systems, software language computers, look-up tables and programs for dedicated microprocessor applications. ROMs can only be read are not written into

- a. MASK ROMs: Mask ROMs are programmed by a masking operation performed on the chip during the manufacturing process. The contents of a ROM are decided by the manufacture. These contents are permanently stored in a ROM at the time of manufacturing. The contents of MROMs cannot be changed by the user. Most desktop computers use MROMs to contain there operating system and for execution fixed procedures, such as decoding the keyboard and the generation of characters for the CRT.

- b. PROMs: If user needs relatively few ROMs, there is a variation, which cost more per devices but allows the user to in rest the information. To avoid the high one-time cost of producing custom mask ROMs, IC manufacturing provides programmable This device ROMs. programmable Read only memory. special Using equipments, called PROM programmers, user can program a PROM- once. Subsequently one can read the information out of PROM as often as one wish, but one can never write into it again. Therefore once the PROM is programmed with correct

information it can be used as a ROM only in microcomputer. If one needs to change or correct the information stored in the PROM, one must pull it out, throw it away and replace is with a fresh unused PROM, writing the corrected information into this unused devices. The PROM will hold its contents indefinitely. These PROMs are provided with fusible links which are burned during the programming. Once the data are permanently stored in the PROMs, it can be read again and again by just accessing the correct memory location.

- (i) EPROMs: If a mistake is done in programming ROM and PROMs, the correction cannot be made. The solution of this problem is erasable PROM (EPROM). An EPROM is an erasable PROM.

- (ii) UVEPROM: It stands for Ultra Violet Erasable Programmable Read Only Memory. The contents are erased by ultra violet light. Therefore, they are also called UVEPROM: The user can not erase the content of a single memory location, the entire contents are erased. EPROMs can be reprogrammed using EPROM programmer. Once programmed, it can be used as ROM in microcomputer. Later, if one needs to correct the information stored, it is taken out from the system, erase the program written, write new program into it and use it. The EPROM is erased by exposing an open window in the IC to an ultraviolet light source for a specified length of time, typical erase time vary between two and 30 minutes, the proper **EPROM** programmed and providing addresses. An EPROM also holds the information indefinitely once it has been programmed. One can read the contents of an EPROM as often as one like.

- 2. RMMs: They are read mostly memories(RMM), since they have much slower write time then read time, there memories are usually suited for operation where mostly reading rather than, sorting will be performed.

- a. E<sup>2</sup>PROMs: E<sup>2</sup>PROM are electrically erasable PROM. They need not to be removed from a microcomputer board for erasing. Erasing & programming E<sup>2</sup>PROM is much easier as the ultraviolet sources are not required. The stored information can be erased by applying a high voltage of about 21V, a singly byte or the entire chip can be erased in10 milli sec. This is faster than UV erasing and it can be done easily while the chip is still in circuit, it is also known as EAPROM (electrically alterable PROM). One can write into at any time without erasing prior contents. The problems with EAROM are that electronically they are relatively difficult to use also, they slowly lose their information. One application

of the E<sup>2</sup>PROM is in the tuner of a modern TV set. The E<sup>2</sup>PROM remember

- (i) the channel, you were watching when your tuned off the set

- (ii) the volume setting of the audio amplifier.

- 3. RWMS: In this type of memory one can either read the contents of an addressed location in a MEMORY READ operation or one can write a m bit of data in the addressed memory location in a MEMORY WRITE operation. It is a volatile memory. It is normally known as RANDOM ACCESS MEMORY (RAM). The content of RWM shall be destroyed when the power is OFF. During of MEMORY READ operation the content of the addressed location is not destroyed. It is only read onto the external data bus. During a MEMORY WRITE operation, however, the original content of the addressed location is destroyed and the new content takes it placed which is just now written. Read/write memories are used for temporary storage of data and program instruction. RWMs are generally called RAMs, RAM is a specific terms which tells that the data can be read on written to any memory location, RAM is classified as:

- a. Static RAM: static RAMs (SRAMs) flip flops as basic storage elements

- b. Dynamic RAM: dynamic RAMs (DRAMs) use internal capacitor as basic storage elements, additional refresh circuitry is needed to maintain the charge on the internal capacitor of a dynamic RAM; they have more packing density, there it has more storage capacity per unit area team a static RAM, the cast per bit of dynamic RAMs is also much less than that of the static RAMs.

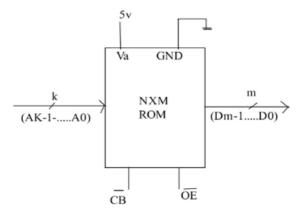

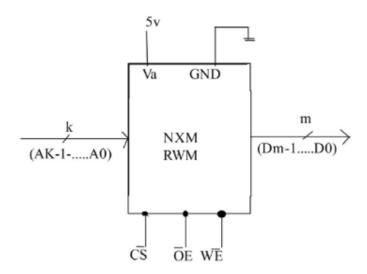

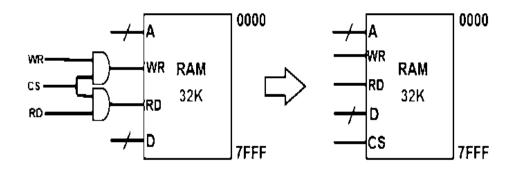

The symbolic diagram of a ROM and RAM ROM are shown in **Figure 28** and **Figure 29** respectively:

Figure 28: Symbolic diagram of ROM

$\overline{CB}$  = Chip selection to control input.

$\overline{OE}$  = output enables signals.

Both the control signals are active low (in general) but they may be active high, when the chip is selected then only addressed memory location data is available on data lines provided  $\overline{OE}$  is active.

Figure 29: Symbolic diagram of RAM

$\overline{CS}$  = Chip selection to control input.

$\overline{OE}$  = output enables signal

$\overline{W}\overline{E} = write \ enable \ signal$

These are representative signal. These signals may be LOW or HIGH for other ROMs. For READ operation, first address is placed and then make  $\overline{CS} = LOW$ , the output is available. Under WRITE operation  $\overline{OE}$  may be HIGH or LOW but  $\overline{WE}$  is active LOW. Under READ operation  $\overline{OE}$  is ACTIVE LOW but  $\overline{WE}$  must be HIGH.

All these memories are random access memories. In RAM any memory location can be accessed in a random fashion without regard to another location. The access time is same for each memory locations.

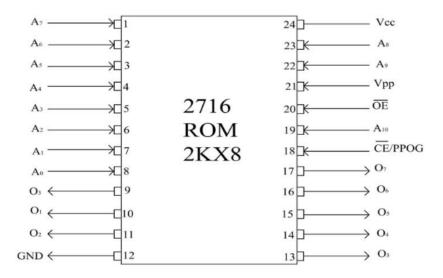

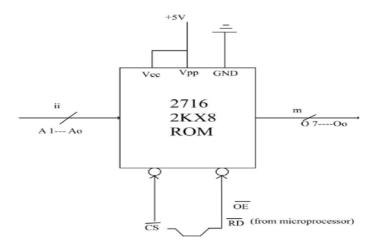

### **2.5 INTEL 2716 EPROM**

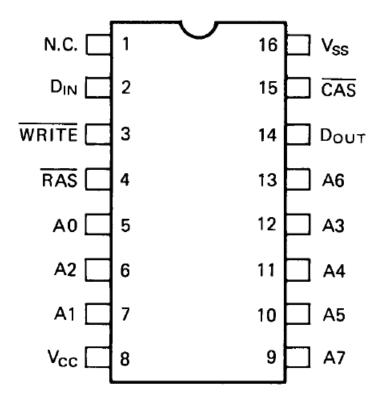

This is an Ultra Violet Erasable Programmable ROM {UVEPROM}. The pin connection & logic symbol is shown in Figure 30 and Figure 31 respectively. It is a 2K  $\,$  X 8 ROM. It has 2048 memory locations. It has 11 address lines. While programming  $V_{pp}$  must be held at 25 volts. If this chip is used in a microcomputer after programming this voltage must be held at +5V.

Figure 30: Intel 2716 pin diagram

The pin details are given below:

$V_{CC}$ , GND = +5V and Ground

$A_{11}$ - $A_0$  = address lines

D<sub>7</sub>-D<sub>0</sub>=data lines

V<sub>PP</sub>=Programming voltage

$\overline{OE}$  = output enables (to enable the output data buffer)

$\overline{CE}/PROG=$  dual function pin. While programming HIGH pulse is applied at this pin and during read operation the chip is selected enabled by making  $\overline{CE}$  pin low.

When it is completely erased then each bit must be '1'. If we want to store '0' we write '0' there.

Before programming each address stores FF<sub>H</sub> but to store any data at the addressed location a 50ms pulse is given to the PROG.

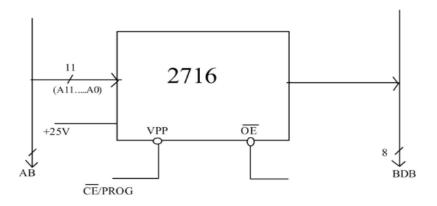

Figure 31: Logic symbolism of Intel 2716

For programming 2716 is connected as shown in figure and following operations are done in sequence:

- 1. Apply 25V dc to pin no  $21(V_{pp})$ .

- 2. Keep the (output enable bar)  $\overline{OE}$  high (+5v).

- 3. Establish the address at the address bus.

- 4. Established the desired data to be stored at the addressed location on the data bus.

- 5. A positive TTL pulse of 50 msec duration is applied to the pin no.  $18 \ (\overline{CE}/PROM)$ .

The waveforms during programming are shown below:

The above procedure is repeated for all location to program all the 2K memory location. One can program 2716 partly as required. All the above actions are carried out in separate unit known as EPROM programmer. It requires only 100sec to program all the memory locations. Once the program is written down in memory chip, it cannot be erased. If we want to change it we put it in UV eraser and erase it and then program it again.

**Figure 32: EPROM Programmer**

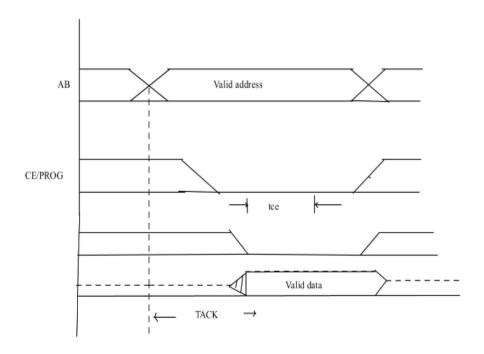

Once the chip is programmed, it can be used to read data again and again. When the two inputs  $\overline{C}\overline{E}$  and  $\overline{O}\overline{E}$  are in their normal state (HIGH) the output is tri-stated(Figure 32). Now, one can only perform a MEMORY READ operation from this device. The following is the procedure for a MEMORY READ operation.

- 1. Establish the addresses of the memory location to be read on the address bus.

- 2. Make the  $\overline{CE}$  signal ACTIVE LOW.

- 3. Apply a  $\overline{R}\overline{D}$  control signal to  $\overline{O}\overline{E}$  terminal i.e. make the  $\overline{O}\overline{E}$  ACTIVE LOW.

$\overline{RD}$  (Read Data Low) is normally set to HIGH by the microprocessor. This is known as MEMORY READ operation. The waveforms during read operation are shown below:

The wave forms of the chip show that the data outputs became valid after a delay for setting up the addresses on enable the chip..

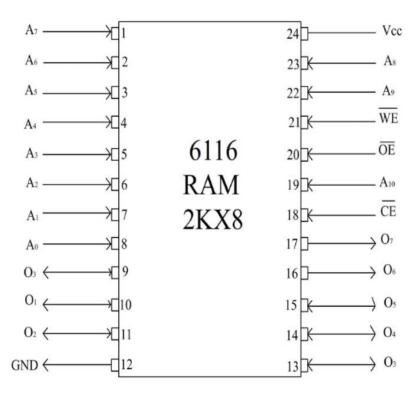

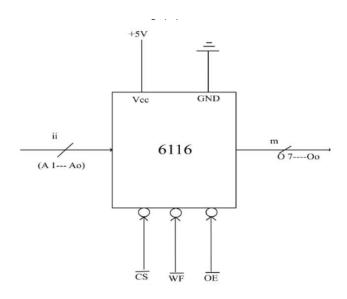

### 2.7 INTEL 6116 RAM

It is 2K X 8 memory. It is a static RWM (2Kx8). This is pin by pin compatible with 2716 ROM. The pin connection is shown in Figure 33 and the logic symbolism is shown in Figure 34.

Figure 33: Intel 6116 RAM

Figure 34: Logic symbolism of Intel 6116 RAM

The truth table for control signals is as follows:

**Table 3 Table for control signals**

| CE | WE | ŌĒ | Operation                      | REMARKS                                                                                                                          |

|----|----|----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | x  | WRITE                          | The data available on the data bus shall be written on the addressed location. The original contents are lost.                   |

| 0  | 1  | 0  | READ                           | The content of the addressed location is READ on to the output data line. The content other addressed location is not destroyed. |

| 0  | 1  | 1  | No<br>operation<br>*tri stated | Output is Tri state.                                                                                                             |

| 1  | *  | *  | No<br>operation<br>tri stated  | Output is Tri state.                                                                                                             |

The two chips 2716 and 6116 are pin by pin compatible and can be used in place of other. The pin by pin compatibility of 6116 with 2716 has a advantage. In the initial stage of a program development we fix up 6116 in the 24 pin socket provided on the microcomputer and develop the program. Once the program is completely tested and satisfactory then using a PROM programmer the program can be transferred to 2716 ROM for permanent storage.

Thereafter, 2716 can be put directly to the same socket occupied by 6116. A simple jumper should be provided for pin no 21. This is shown below.

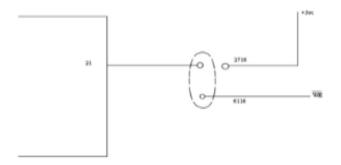

### 2.6 DYNAMIC RAM CHIP

A dynamic RAM comprises storage cells that may be thought of electically as capacitors. There are many thousands of these capacitors, or storage cells on a dynamic RAM chip, each all is capable of storing one bit of information.

The capacitor that makes this storage cell is not ideal. That is, charge placed on this capacitor will leak off given enough time. In a DRAM, the charge on the capacitor represents the stored data. Therefore, the data stored in the cell can be lost. A more accurate model of the storage cell is a capacitor in parallel with a resistor(Figure 35).

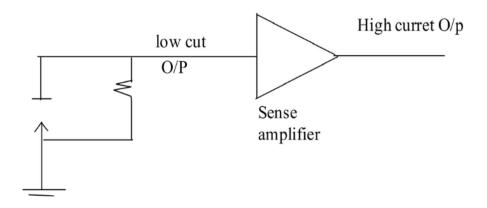

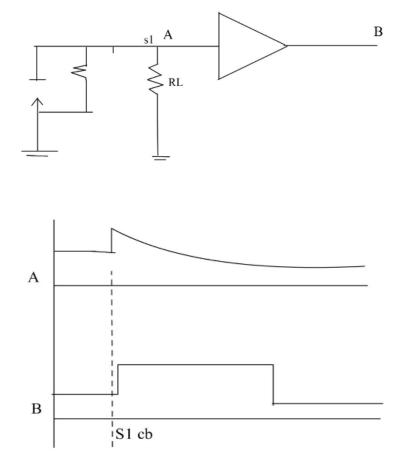

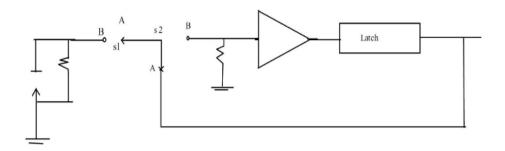

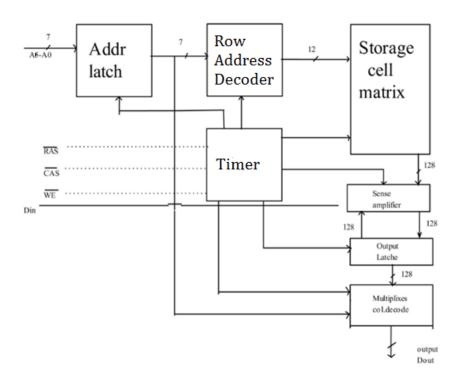

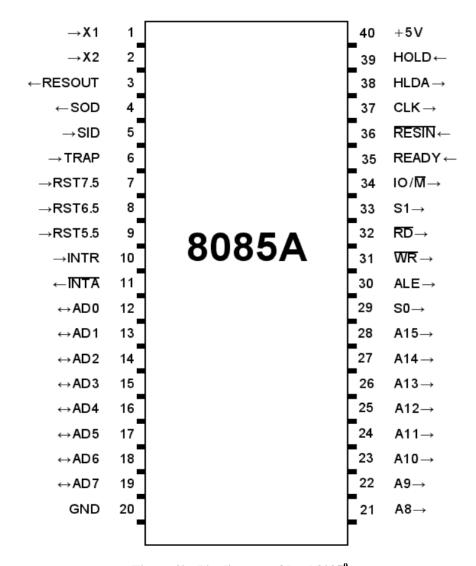

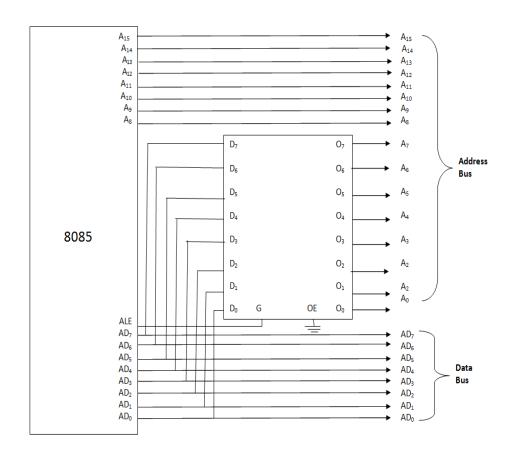

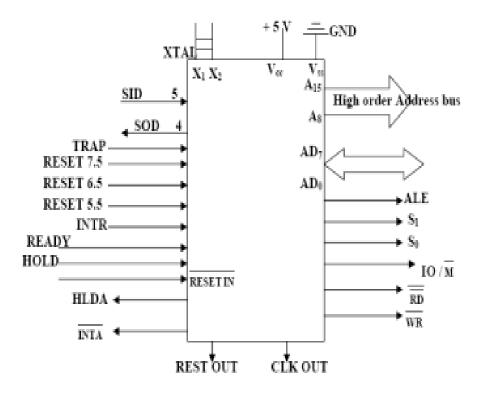

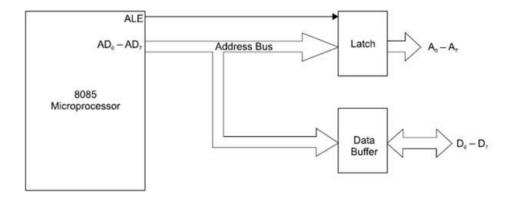

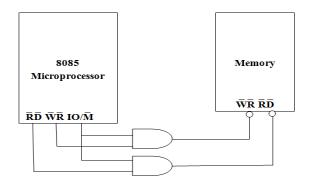

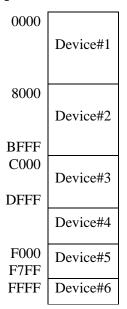

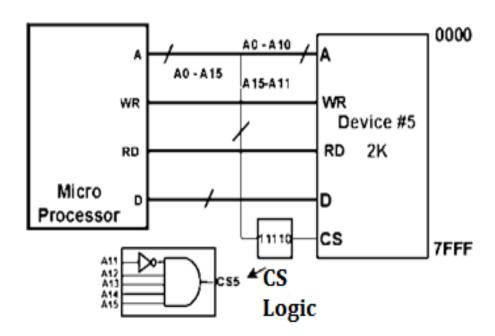

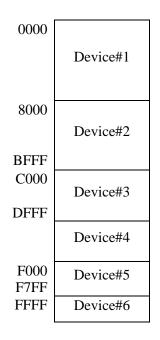

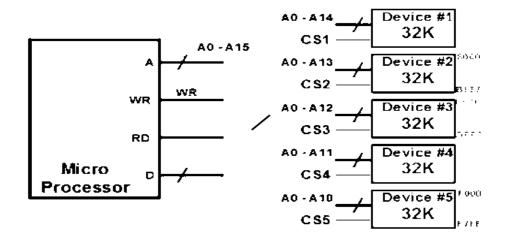

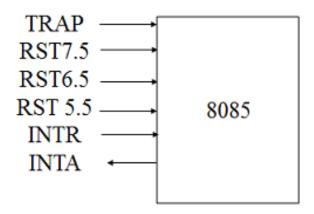

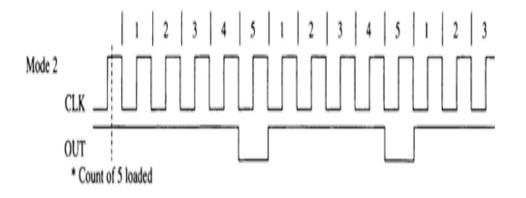

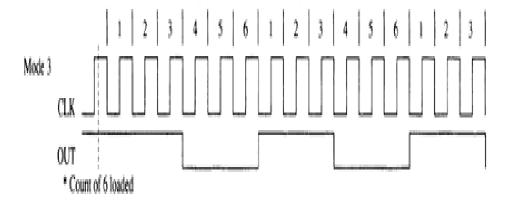

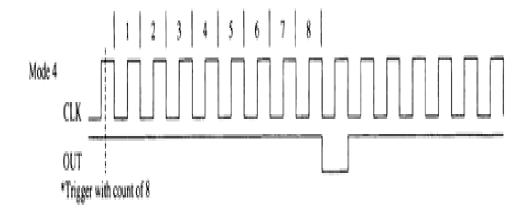

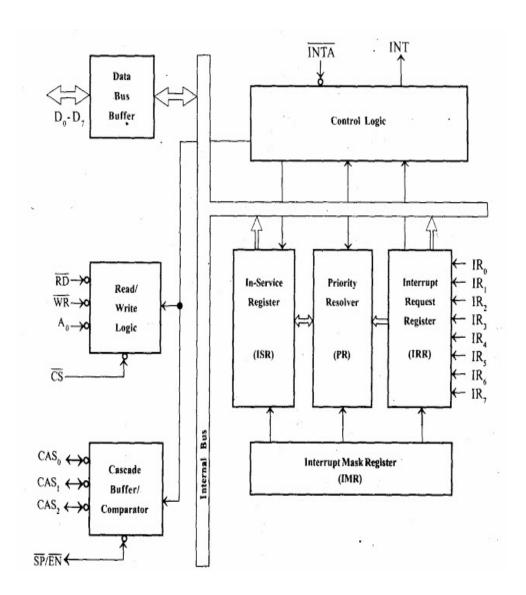

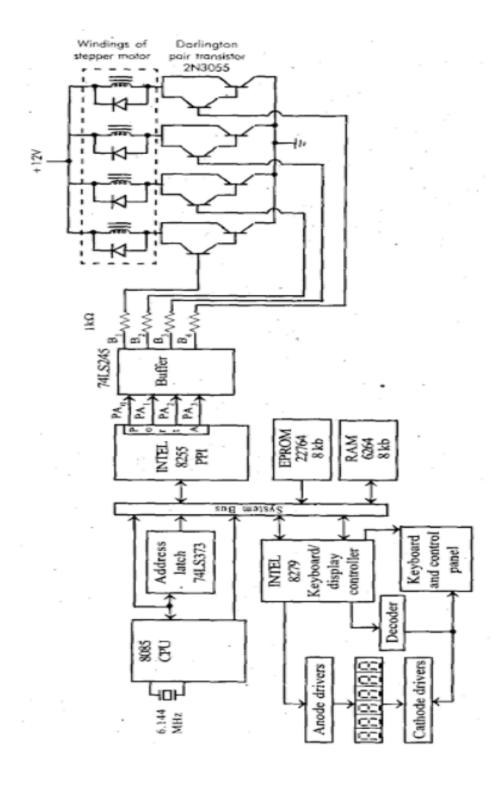

Figure 35: Capacitor